AMD Zen5銳龍9000核心佈局解密:512位浮點單元大變

2024-10-11 10:53:21 6

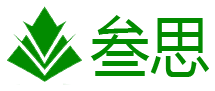

快科技10月7日訊息,Nemez、Fitzchens Fitz、HighYieldYT等多位大神共同完成了Zen5架構銳龍9000系列的核心解密,包括高畫質照片、模組分佈圖。

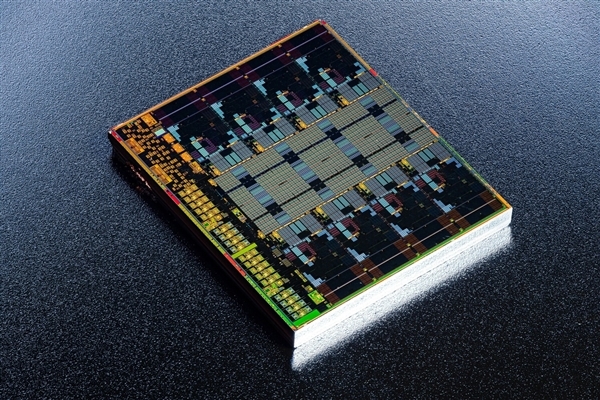

銳龍9000系列延續了chiplet佈局,包括一顆或兩顆CCD、一顆IOD。

其中,CCD升級架構的同時,製造工藝也從N5 5nm升級為N4P 4nm,IOD則和銳龍7000系列上的完全一樣,工藝也還是N6 6nm。

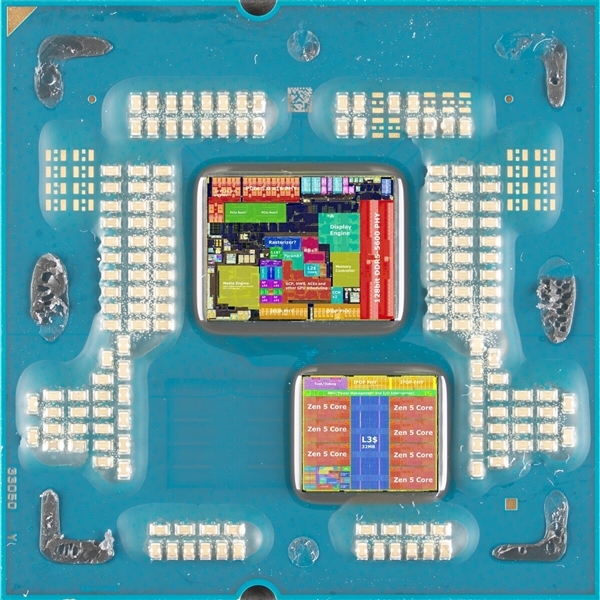

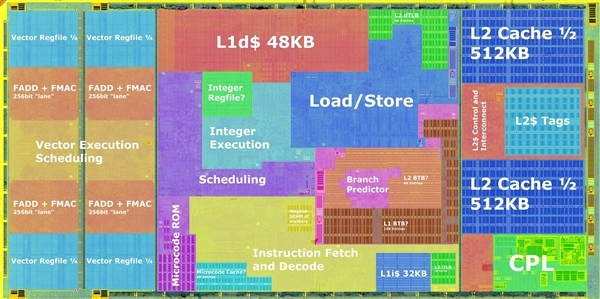

CCD整體佈局如上,包括左右兩排一共八個Zen5 CPU核心,夾在中間的所有核心共享的32MB三級快取。

注意看,三級快取的兩排粉色長條區域,和以往一樣,是為3D快取預留的TSV矽通孔,銳龍9000X3D系列上會用到它。

下方是系統管理單元(SMU)、電源管理單元(PMU)、I/O互聯模組,以及兩個Infinity Fabric高速互連通道模組(IFoP),EPYC上它們的作用更大。

左下角紫色的區域,被標註為測試/除錯之用。

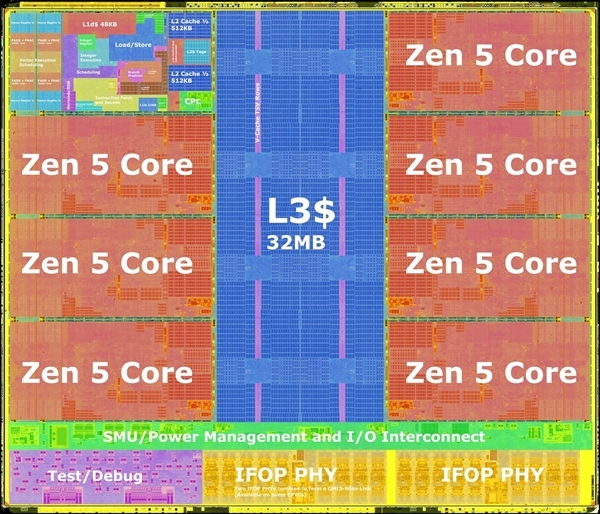

細看每個核心,左側大片區域是向量執行單元,主要用作浮點操作,完整支援512位浮點路徑,可用於AVX-512指令,所以面積相當大,而且位於核心以及整個CCD的邊緣,因為浮點運算發熱量大,這樣方便散熱。

右側是二級快取,與之相連的就是三級快取。

中間部分可以看到指令預取與解碼、分支預測、微操快取、排程器等組成的最重要的前端模組,以及32KB一級指令快取、48KB一級資料快取、整數執行單元、載入/儲存單元。

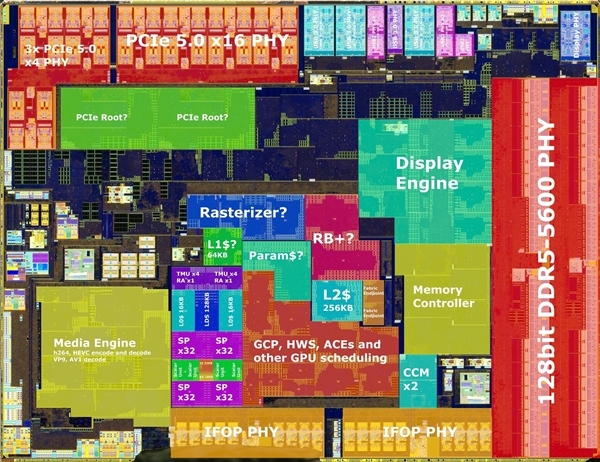

IOD部分沒啥新鮮的,128個流處理器的GPU核心、顯示引擎、多媒體引擎、128-bit DDR5-5600記憶體控制器、28條PCIe 5.0控制器、USB 3.x/2.0控制器、兩個IFoP埠。

是的,沒有原生USB4,X870E/X870上的介面都來自板載第三方主控。

本站內容由互聯網用戶自發貢獻,該文觀點僅代表作者本人。本站僅提供信息存儲空間服務,不擁有所有權,不承擔相關法律責任。如發現本站有涉嫌抄襲侵權/違法違規的內容,請發送郵件至舉報,壹經查實,本站將立刻刪除。