晶片製造,新拐點?

2024-10-21 01:32:52 3

當與可圖案化金屬(如 Ru)結合使用時,半鑲嵌(semi-damascene)有望實現 RC、面積、成本和功率效率,以提供互連縮放路徑。

1997 年,邏輯和記憶體晶片後段 (BEOL:back-end-of-line) 中引入了 CU 雙大馬士革(CU DUALdamascene)整合方案,標誌著半導體歷史上的一個轉折點。晶片製造商從減法鋁圖案化(subtractive Al patterning)轉向溼法工藝,如銅電鍍和化學機械拋光 (CMP)。這種徹底的轉變是為了應對鋁基互連中不斷增加的 RC 延遲,這是電阻電容 (RC) 乘積增加的結果。Cu 雙大馬士革具有成本效益,適用於 BEOL 堆疊的多層,有望實現許多後續邏輯和記憶體技術。

但幾年後,最關鍵的 BEOL 層內的金屬間距將降至 20nm 以下。當這種情況發生時,Cu 雙大馬士革將失去動力。隨著金屬線尺寸的縮小接近 Cu 的電子平均自由程,RC 延遲將急劇增加。此外,Cu 金屬化需要屏障、襯墊和覆蓋層,以確保良好的可靠性並防止 Cu 向外擴散到電介質中。但這些額外的層開始消耗總可用線寬的很大一部分,這意味著互連金屬本身無法充分利用寶貴的導電面積。這些問題迫使晶片行業研究在緊密金屬間距下具有更好效能係數的替代金屬化方案。

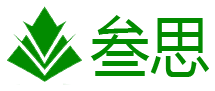

在 2017 年提交初始專利後,imec 於 2020 年向半導體界提出了一種新的金屬化概念,並將其命名為“半鑲嵌”(semi-damascene)。與基於 Al 的金屬化一樣,半鑲嵌整合從第一個區域性互連金屬層的直接圖案化(或減法金屬化)開始,因此需要可圖案化的金屬,例如 W、Mo、Ru 等(圖 1)。然後以單鑲嵌方式對與下一個互連層連線的通孔進行圖案化:在電介質中蝕刻的孔用金屬填充並過度填充 - 這意味著金屬沉積持續進行,直到在電介質上形成一層金屬。隨後對該金屬層進行掩蔽和蝕刻以形成第二互連層,其線條與第一層正交。

半鑲嵌的價值主張很有前景。它可以被視為一種雙層金屬化模組,可能可擴充套件到多層——從而具有成本效益。減法蝕刻允許比傳統 Cu 互連更高的金屬線縱橫比 (AR),從而改善電阻。至於電介質,金屬線可以與氣隙結合,而不是低 k 電介質間隙填充。氣隙提供較低的介電常數,從而導致較小的層內電容。除了具有 RC 效率外,半鑲嵌還消除了金屬 CMP 的使用,簡化了工藝流程並改善了線高控制。使用難熔金屬也有好處。它們有望在不使用阻擋層的情況下使用,從而提供低通孔和線電阻。它們還更耐電遷移,並且在減小尺寸的情況下總體上比 Cu 提供更低的電阻。

一項有前途的顛覆性技術

自從 imec 引入半鑲嵌整合以來,多個組織開始研究類似的新方案,並透過模擬和實驗取得了穩步進展。如今,該方案的第一步,即第一金屬層的減法蝕刻,已由多個組織在會議上成功演示和報告。實驗清楚地表明,在第一個區域性互連層中用減法蝕刻的 Ru 代替 Cu 已經可以提供非常想要的好處,即使在適度的線 AR ~2 下也是如此。對於後續幾代,AR 可以增加到 3 或 6,然後組合成多個區域性金屬層。越來越多的研發證據表明,半鑲嵌確實是一個有效的選擇,提供了互連縮放路徑。

與此同時,也存在一些疑問。業界目前正在考慮將第一代半鑲嵌工藝推進到開發階段,即實際生產之前的階段。與任何新技術一樣,行業不會一蹴而就。半鑲嵌整合顛覆了製造 BEOL 的傳統技術。它需要新的工具和材料,而且可能有些缺陷機制在研究階段沒有被捕捉到。只有當該技術能夠跨越幾代技術時,這種投資才有意義。雖然第一步只有一層金屬層已經得到充分記錄,但兩層甚至多層整合方案的實施——可以充分利用半鑲嵌的能力和優勢——卻討論得較少。這就是為什麼 imec 鼓勵研發界展開討論,幫助填補剩餘的“空白”,並在互連技術會議上分享關於多層整合的見解。

imec 互連路線圖

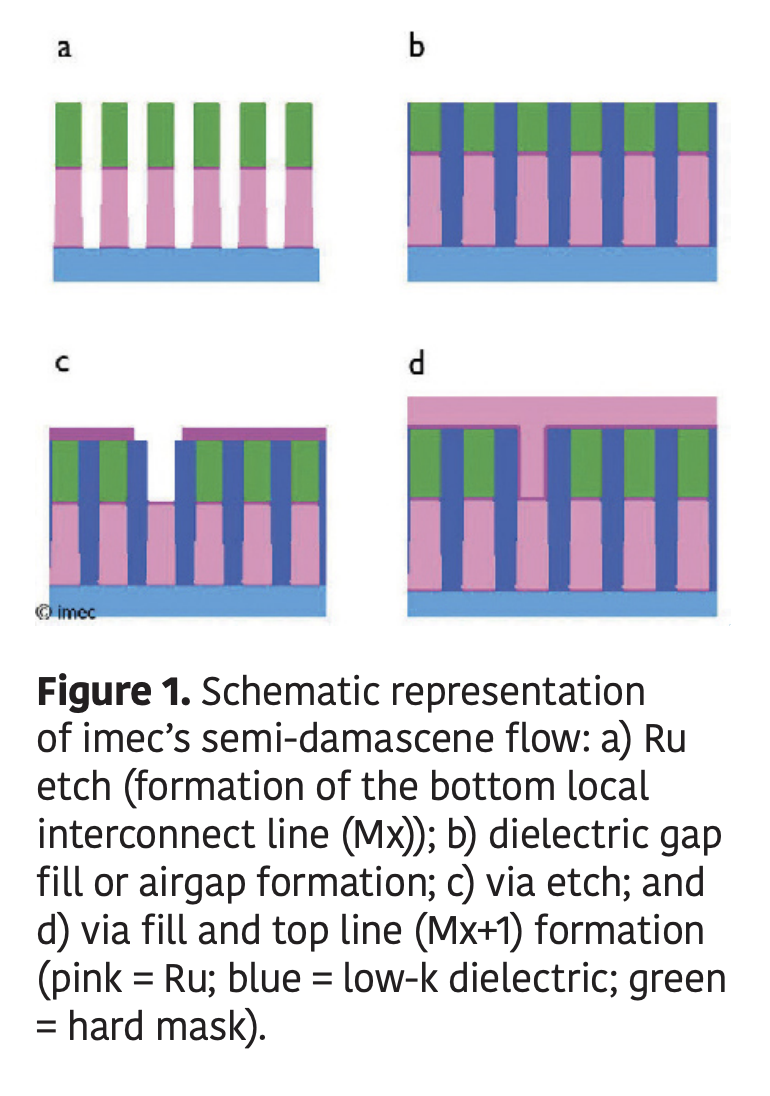

Imec 提議逐步引入後續幾代半鑲嵌技術。第一代半鑲嵌技術預計將用於 imec A10 或 A7 邏輯技術節點,其中最關鍵互連的金屬間距將達到 18nm(圖 2)。屆時,GAA 奈米片整合有望成為主流,而 CFET 尚未到位。因此,引入半鑲嵌技術將是晶片製造商必須應對的唯一重大變化。

Imec 提議在 M0 中引入減法蝕刻的 Ru,這是沿線中點 (MOL:middle of line) 的第一個區域性金屬層。第一代產品將採用金屬線 AR 2,略高於當今典型的 Cu 線 AR(~1.6)。結合無阻擋 Ru 在緊密金屬間距下的良好效能,這種方法已經比 Cu 具有更好的電阻和可靠性。

在第二代中,imec 的目標是將 M0 互連線的 AR 增加到 3,這將進一步降低電阻,並將 M0 與無阻擋通孔相結合。由於較高的 AR 往往會增加層內電容,因此這一代需要氣隙而不是低 k 介電間隙填充。除了提供較低的介電常數外,使用氣隙還可以避免“間隙填充問題”:以均勻的方式用電介質填充窄溝槽的挑戰。

透過以半鑲嵌方式新增通孔和第二層金屬層,第三代將實現真正的半鑲嵌整合,M0 和 M2 區域性金屬層(BEOL 中最關鍵的層)。第四代可能會看到更多的半鑲嵌層。AR 將逐漸增加到 4、5 甚至更多 - 具體取決於可行性。當與氣隙結合時,預計最高可達 ~AR=6,與其他選項相比具有足夠的 RC 優勢(圖 3)。

從長遠來看,我們稱之為第五代,imec 設想替代金屬將進入半鑲嵌路線圖。考慮可圖案化的二元或三元化合物,它們在緊密的互連間距下具有比單一金屬更好的品質因數。

因此,半鑲嵌工藝可以成為 BEOL 製造的下一個轉折點。它具有極佳的價值主張,不僅在電阻、電容和麵積消耗方面。實驗和模擬還表明,與 Cu 雙鑲嵌方案相比,它的功耗更低,熱效能更好。同時,如上所述的分步實施將允許最大限度地降低引入新技術所帶來的風險。

實現先進半鑲嵌工藝

雖然第一代和第二代已準備好進入開發階段,但仍需要進行更多研究來展示和完善下一代半鑲嵌技術。主要挑戰可以歸結為多層半鑲嵌整合、AR 的增加以及第五代新金屬的探索。

以下是 imec 研究人員報告的最新進展。這些結果不僅旨在填補剩餘的空白。他們還旨在引發討論並鼓勵其他研究機構補充 imec 的研究——以造福整個生態系統。

邁向先進互連的多層整合方案如前所述,半鑲嵌本質上是一種兩金屬層整合方案,可能可擴充套件到多層。但多層方案的工藝最佳化仍處於起步階段。實現它們的最佳方法是什麼?應該使用哪些光刻和蝕刻工藝、硬掩模和抗蝕劑?以及如何整合連線後續 BEOL 層極窄互連線的通孔?

為了解決最後一個問題,imec 早些時候提出了完全自對準通孔 (FSAV:fully self-aligned

via) 作為半鑲嵌的關鍵構建塊。FSAV 確保線路和通孔(通孔頂部和底部)的正確對齊,這對於實現低通孔到線路洩漏至關重要。到目前為止,包括 imec 在內的多個研究機構已經提出了幾種 FSAV 整合方案。

在 IITC 2024 上,imec 率先對不同的 FSAV 整合選項進行基準測試(圖 4),旨在探索如何在 300 毫米晶圓廠中最好地實施 FSAV 。換句話說:我們如何才能透過最佳的通孔到線覆蓋來滿足目標通孔電阻,同時確保整個 300 毫米晶圓的低變異性和良好的可重複性?

除了傳統的單鑲嵌方案 (FSAV) 來建立通孔(即透過在 SiO2 電介質中蝕刻一個孔然後用金屬填充來建立通孔)之外,imec 還探索了兩種基於柱的 FSAV 整合方案(即透過直接蝕刻金屬層將通孔形成為柱)。這兩種變體被稱為“混合柱”(HP-FSAV)和“帶有蝕刻停止層的柱”(PE-FSAV)。

三種整合方案在工藝步驟數量、所用的圖案化和蝕刻工藝、硬掩模整合和光刻膠型別(例如,允許 EUV 光刻色調反轉以啟用支柱)方面有所不同。但對於這三種情況,都展示了達到目標通孔電阻和通孔到線覆蓋裕度的可行性(圖 5)。最顯著的差異與整個晶圓上實現的電阻均勻性有關。所有整合方案都提供了足夠的通孔光刻和蝕刻工藝視窗。因此,它們與我們工具供應商目前提供的直接金屬蝕刻裝置相容。imec 的其他研究表明,自對準視窗也可用於實現氣隙,當線路 AR 進一步增加時,這將需要繼續發揮電容優勢。

因此,今天的現狀證明,至少有兩層半鑲嵌技術在技術上是可行的。同時,展示的晶圓數量有限。因此,imec 鼓勵其他組織補充這一難題,讓行業生態系統“決定”最佳選擇。

逐步增加半鑲嵌線的縱橫比:理解和緩解障礙。透過進一步增加其 AR,可以持續降低 Ru 半鑲嵌線的電阻。2022 年,imec 首次展示了證據,證明使用 AR 6 的半鑲嵌(圖 6)確實可以顯著提高 RC 指標,優於較低 AR 方案。不久之後,初步實驗表明,高 AR 線也與多層方案相容。

雖然人們對具有適度 AR(2 和 3)的互連線的形成了解得比較清楚,但要提高 AR 並保持良好的線路電阻和可靠性,需要掌握一些技術。事實證明,這幾乎挑戰了每個工藝步驟——包括圖案化和蝕刻、清潔和缺陷控制。例如,直接金屬蝕刻會“攻擊” Ru 線的側壁,導致線路斷裂缺陷。而且這種情況會隨著 AR 的增加而惡化。要獲得儘可能低的線路電阻,就需要對高 AR 線路的形成和可靠性有更基本的瞭解。

作為第一個重要見解,imec 的研究人員發現,用於形成高 AR 金屬線的堆疊成分對半鑲嵌線的電阻有很大影響。線路斷裂缺陷被證明是影響堆疊相關裝置效能的主要因素。Imec 透過多次實驗找到了最佳堆疊,首先沉積 1nm TiN 以提高粘附性,然後進行物理氣相沉積 (PVD) Ru。與研究中使用的其他成分相比,該堆疊在整個金屬線高度上提供最低的電阻。其次,該研究首次表明,線缺陷受 Ru 金屬晶粒的晶粒結構和晶體取向的影響。這些形態引數在很大程度上取決於用於沉積 Ru 的方法,有利於使用 PVD。

除了深入瞭解影響 Ru 線電阻的引數外,imec 最近還提出了一種獨特的方法,從電阻和均勻性的角度進一步改善高 AR 線:在兩個 Ru 層之間夾一層亞奈米 TiN 或 W 層。與沒有此額外層的堆疊相比,這種堆疊在直接金屬蝕刻過程中不易受到橫向攻擊和形成斷線。這種“缺陷緩解層”的主要好處是,它能夠實現高 AR 和長長度的低缺陷線,這對AR>6的 Ru 半鑲嵌來說是一個有希望的方向。結果在 2024 年 VLSI 研討會上進行了展示。

實驗工作表明,在 24nm 間距以下的線路上具有良好的可靠性行為(圖 7)。但同時,還需要開展更多工作來最佳化和擴充套件結果以達到 18nm 間距,展示與整合氣隙的相容性,並展示足夠的時間相關電介質擊穿 (TDDB:time-dependent dielectric breakdown) 和機械可靠性裕度。

先進互連:尋找替代導體。到目前為止,半鑲嵌整合方面的工作主要集中在使用 Ru 作為首選導體。幾年前,imec 開始研究是否有其他具有更好前景的金屬。搜尋範圍從元素金屬擴充套件到二元和三元有序化合物 。在一項有希望的初步研究之後,全球多個研發小組開始接受這個想法,並加入了尋找候選合金的行列。該社羣最近聚集在 VLSI 2024 專題研討會上,主題為“用於先進互連的新型金屬”。該研討會由 imec 組織,旨在從工業和學術角度討論最新技術和未來的研究方向。

由於潛在合金的清單非常龐大,imec 開始研究時建立了一種獨特的方法來篩選和排列可能的候選材料。確定了兩個與 Cu 對比的優值:化合物的內聚能以及體電阻率與載流子平均自由程的乘積。從頭算模擬揭示了一個候選材料的子列表,例如金屬間鋁化物,這是進一步實驗工作的起點。

如今,世界各地的研究小組都在研究這些候選合金在縮小尺寸時電阻率的表現。例如,當金屬間鋁化物沉積在薄膜中時,薄膜形成過程中涉及的缺陷機制似乎會影響電阻率行為(圖 8)。瞭解這種相關性將是控制電阻的關鍵。Imec 還認為,整體和區域性成分控制是最小化電阻的重要手段。

一旦找到最佳化有前景的二元和三元合金電阻的方法,下一步就是將其應用於相關的金屬化方案,並解決與半鑲嵌工藝相關的挑戰。Imec 鼓勵大學和研究小組合作探索圖案化和蝕刻策略,並制定工藝方向。儘管還有很多工作要做,但替代金屬的研究是一個有前途的途徑,而且正在取得穩步進展。仍需要密切合作,最終將它們引入第五代半鑲嵌整合。

結論

半鑲嵌金屬化可能成為 BEOL 製造的下一個轉折點,目前業界正在討論在第一個區域性互連層中引入減法蝕刻。儘管第一代半鑲嵌技術目前尚未投入生產,但根據實驗證據,imec 已經開始展望新一代半鑲嵌技術。重點是多層金屬和通孔、逐步增加縱橫比以及引入新金屬。要使這些下一代技術成為現實,需要學術界和工業界的共同努力和更多資料以及強有力的投入。

本站內容由互聯網用戶自發貢獻,該文觀點僅代表作者本人。本站僅提供信息存儲空間服務,不擁有所有權,不承擔相關法律責任。如發現本站有涉嫌抄襲侵權/違法違規的內容,請發送郵件至舉報,壹經查實,本站將立刻刪除。